So erstellen Sie einen einfachen seriellen UART-Transmitter in verilog HDL

Die meisten Universal Asynchronous Receiver Transmitter (UART), die ich online gefunden habe, sind zu kompliziert und schwer zu verstehen. Hier werde ich eine einfache Theorie erklären und auch Code zum Erstellen eines solchen.

Lassen Sie uns zunächst darüber sprechen, wie Sender funktionieren. Das Grundprinzip besteht darin, mehrere Datenbits über eine einzige Leitung zu senden. In unserem Sender sind diese Daten parallel, aber um die Anzahl der erforderlichen Drähte zu reduzieren, verwenden wir eine serielle Kommunikation, die am Empfängerende in parallel umgewandelt wird.

Die grundlegenden Dinge, die wir brauchen, sind die folgenden:

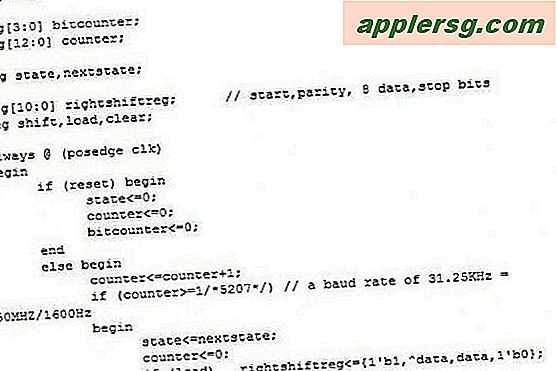

- Ein Taktteiler (unser Zähler)

Dies ermöglicht es uns, Daten mit einer bestimmten Geschwindigkeit (Baudrate) zu senden. Unser Empfänger wird die Daten Bit für Bit abtasten und aufnehmen.

- Ein Schieberegister

Wir müssen wissen, wie viele Bits wir gleichzeitig übertragen. Unser Schieberegister hat ein Startbit, Datenbits, Paritätsbit (optional), Endbit.

- Ein Zustandsdiagramm

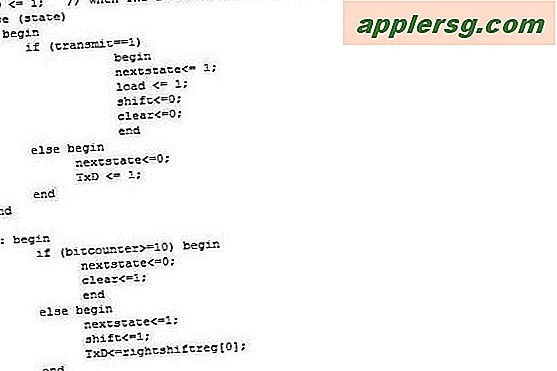

Bevor wir Code schreiben, müssen wir uns überlegen, was wir erstellen müssen, und der beste Weg ist, ein Zustandsdiagramm unseres Designs zu erstellen. Wir wissen, dass wir für einen Sender 2 Zustände benötigen, IDLE und TRANSMITTING.

Nachdem wir ein Zustandsdiagramm haben, können wir jetzt berechnen, was unser Zähler sein wird. Dies geschieht durch die Verwendung von:

Zähler = FPGA-Takt/Baudrate

In diesem Beispiel verwende ich eine Baudrate von 9600, wodurch mein Zähler = 5208 ist.

Zuletzt berechnen wir unser Schieberegister und beenden das Schreiben unserer Zustandsmaschine. In meinem Beispielcode verwende ich ein Startbit, ein Paritätsbit, 8 Datenbits und ein Endbit. Das sind insgesamt 11 Bit.

Beide Bilder in Schritt 2 und 3 zusammen im selben Modul vervollständigen unseren Sendercode, der für die Programmierung auf dem FPGA erforderlich ist. Dieser Code funktioniert unter anderem mit einem anderen seriell angeschlossenen FPGA oder mit Windows-Hyperterminal. Kann leicht geändert werden, um mit viel mehr zu arbeiten.

Zuletzt erstellen wir einen Testadapter, um Fehler zu beheben und unser Programm zu simulieren, bevor wir das FPGA programmieren.

Damit ist der Sender abgeschlossen. Bitte hinterlassen Sie Kommentare, wenn Sie Fragen haben oder das Gefühl haben, dass hier etwas fehlt.

Tipps

Sowohl Sender als auch Empfänger müssen die Baudrate kennen, mit der Daten gesendet werden.